In den vergangenen Jahren wurden wir Zeugen einer anhaltenden Weiterentwicklung elektronischer Baugruppen, die durch eine zunehmende Zahl neuer Funktionen, Schnelligkeit und eine extrem kompakte Größe überzeugen. Elektronische Baugruppen früherer Generationen nutzten Steuer-, Daten- und Taktsignale mit niedrigeren Frequenzen, höheren Spitze-zu-Spitze-Amplituden und besseren Störfestigkeiten – kurz gesagt, sie waren einfacher zu konzipieren. Auf Aspekte, die heute von höchster Bedeutung sind wie Impedanzkontrolle, Leitungsterminierung, Nebensignaleffekte und Signalintegrität wurde weniger Wert gelegt. Heute müssen selbst Hardware-Entwickler die mit Hochfrequenzsignalen in Verbindung stehenden Aspekte bereits bei der ersten Leiterplattenentwicklung berücksichtigen. Eine Leiterplatte für Hochfrequenzsignale besitzt eine höhere Dichte an hochintegrierten Bauteilen, was den Einsatz mehrlagiger Leiterplatten, welche die Interferenz zwischen Signalen und parasitären Induktivitäten reduzieren und die Masseverbindungen verbessern, zwingend erforderlich macht.

Hochgeschwindigkeitsleiterplatten

Nicht alle Leiterplatten, die mit digitalen Signalen arbeiten, müssen zwangsläufig Hochgeschwindigkeitsleiterplatten sein. In vielen Fällen reicht es aus, bei der Layoutgestaltung Standardregeln und -grundsätze zu befolgen: Positionierung und Anordnung der elektronischen Bauteile, Festlegung der Signallagen, Powerplane und Massefläche, Aufnahme zusätzlicher Durchkontaktierungen oder automatisches Leiterbahn-Routing. Eine Leiterplatte für Hochfrequenzsignale dagegen erfordert ein akkurates und spezifisches Design, das Signalintegrität unter allen Betriebsbedingungen gewährleistet. Dies ist einer der Gründe, warum die Hersteller von Bauteilen für hochdichte und hochfrequente Leiterplattendesigns (FPGAs, GPUs, SoCs und RF-Module) das Evaluation Board selbst entwerfen und liefern. Generell kann eine Leiterplatte als "Hochgeschwindigkeitsleiterplatte" gelten, wenn die Signalumschaltung bei Frequenzen der Größenordnung Mega- oder Gigaherz erfolgt. In diesen Fällen müssen spezielle Regeln des Leiterplattendesigns zu den Grundregeln, die allen Leiterplattentypen gemeinsam sind, hinzukommen:

- Die durch das Stromverteilungsnetz (vor allem in Gegenwart von Schaltnetzteilen) generierten Geräusche eindämmen;

- Nebensignaleffekte zwischen benachbarten Leiterbahnen reduzieren; Bei einer hohen Signalfrequenz entstehen leicht kapazitive Nebensignaleffekte, da die induzierten Ströme eine kapazitive Impedanz besitzen;

- Die durch das Prellen der Erdreferenz entstehenden Effekte reduzieren (Ground Bounce). Diese direkt mit dem Problem der Signalintegrität zusammenhängenden Effekte werden durch die angemessene Festlegung des Lagenaufbaus und die Entkopplung der einzelnen Leiterplattenteile reduziert (zum Beispiel Trennung zwischen logischen und analogen Bereichen);

- Eine optimale Impedanzanpassung anstreben;

- Beseitigung des häufig durch zu enge Bahnen verursachten vorübergehenden Ringing-Effekts;

- Für die korrekte Terminierung jeder Signalleitung sorgen; Zusammen mit der Steuerung von Eingangs-, Last- und Übertragungsimpedanz ermöglicht dieser Aspekt die Beseitigung der Signalreflexion;

- Hohe Störfestigkeit gegenüber elektromagnetischer Interferenz (EMI), sowohl bei leitungsgeführten als auch bei abgestrahlten Störungen.

Designrichtlinien

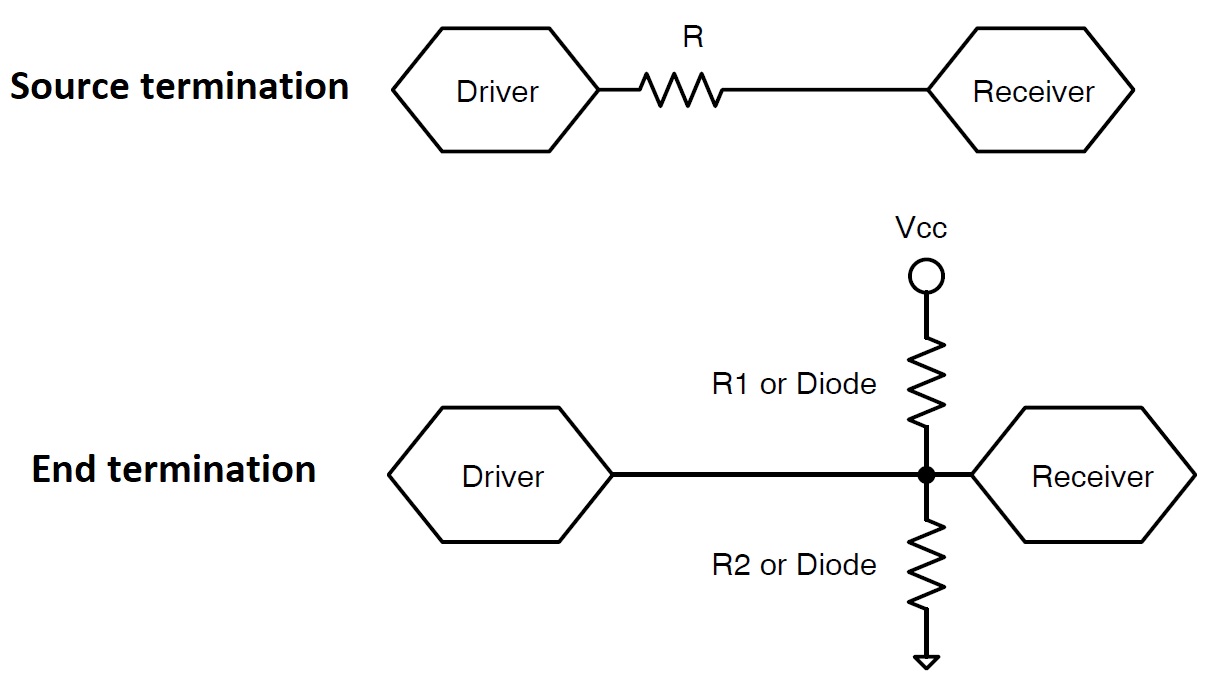

Ein erster zu berücksichtigender Designaspekt betrifft die Impedanzkontrolle. Die kritische Anstiegszeit einer Hochfrequenzleiterplatte in der Größenordnung weniger Nanosekunden stellt die Mindestumschaltzeit dar, unter der kein Leiterplattensignal abklingen darf. Diese Zeit hängt vom Impedanzunterschied zwischen den Enden der einzelnen Bahnen ab, der umso höher ausfällt, je länger die Bahn ist. Sind die Leiterplattenbahnen nicht sehr kurz, muss die Impedanzanpassung für jede Bahn beim Routing erfolgen, um Signalreflexionen zu beseitigen. In jedem Fall muss selbst bei kurzen Bahnen die Signalintegrität gewahrt werden. Dieses Ziel lässt sich durch die ordnungsgemäße Terminierung der Leitungen und eine korrekte Lagenaufbaudefinition erreichen. Im Wesentlichen existieren zwei Terminierungstechniken: Quell- und Endterminierung. Wie in Abbildung 1 gezeigt, beruht die Quellterminierung auf der Reihenschaltung eines Widerstands mit der Übertragungsleitung, möglichst nahe an der Quelle platziert. Der RS-Wert des Terminierungswiderstands muss folgende Bedingung erfüllen: RD + RS = Z0, wobei RD die Ausgangsimpedanz der Leitung und Z0 die Impedanz der Übertragungsleitung ist. Diese Technik beseitigt Signalreflexionen, da die reflektierte Welle auf dem Weg zurück zur Quelle absorbiert wird. Endterminierung nutzt dagegen einen am Endpunkt der Leitung angebrachten Widerstand in Pullup- oder Pulldown-Konfiguration. Der Widerstandswert muss mit dem der Übertragungsleitung übereinstimmen.

Abb. 1: Die beiden Signalterminierungsmethoden.

Sehr wichtig ist die Auswahl der Materialien und die Festlegung des Leiterplatten-Lagenaufbaus. Generell kann für Frequenzen unter einem Gigaherz ein kostengünstiges und häufig verwendetes Substratmaterial wie FR-4 verwendet werden. Dabei muss jedoch beachtet werden, dass die Geschwindigkeit, mit der sich ein Signal auf der Leiterplatte bewegt, von der Dielektrizitätskonstanten des spezifischen Materials abhängt. Verändert sich diese Konstante (Dk) mit der Frequenz, erreichen verschiedene Signalbestandteile die Last zu unterschiedlichen Zeiten, wodurch Signalverzerrungen entstehen. Aus diesem Grund werden für Frequenzen über 1 GHz Materialien wie Laminate von Rogers verwendet, welche im Frequenzbereich zwischen 0 und über 15 Ghz eine einheitliche Dielektrizitätskonstante sowie eine hervorragende Wärmeableitung sicherstellen.

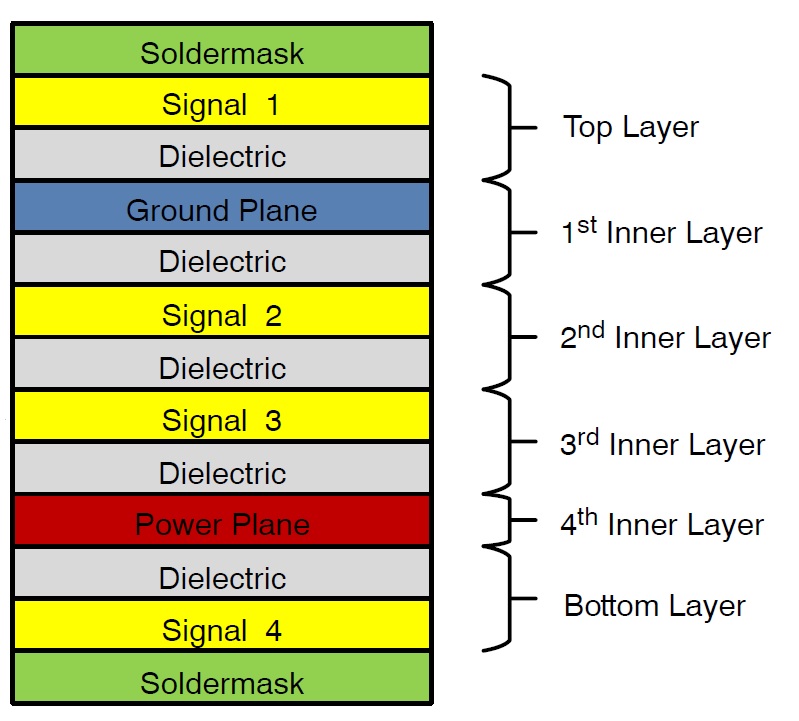

Bezüglich des Lagenaufbaus einer mehrlagigen Hochfrequenz-Leiterplatte kommt es vor allem darauf an, die Hochfrequenzsignale in die inneren Schichten, neben einer Bezugsebene (Massefläche oder Powerplane) zu platzieren, damit ein Schutzschild gegen von außen kommende Strahlung existiert. Außerdem muss vermieden werden, dass sich zwei Hochfrequenzsignale auf benachbarten Lagen befinden: dazwischen immer eine Bezugsebene als Trennung einfügen. Massefläche und Powerplane müssen voneinander getrennt werden; wenn möglich, sind mehr Masseflächen vorzusehen, um Impedanz und asymmetrische Strahlung zu verringern. Abbildung 2 zeigt ein Beispiel eines sechslagigen Leiterplatten-Lagenaufbaus für Hochfrequenzsignale. Der Lötstopplack hilft, den Impedanzwert zu senken, während für die dielektrischen Ebenen Materialien und Substrate wie Rogers oder ähnliches verwendet werden.

Abbildung 2: Beispiel eines 6-lagigen Lagenaufbaus.

Bei der Festlegung des Leiterbahnen-Layouts bzw. des Routings ist besondere Vorsicht angesagt. Um Nebensignaleffekte zu reduzieren, muss zunächst der Abstand zwischen den Signalbahnen so weit wie möglich vergrößert werden und sie müssen in der Nähe der Massefläche platziert werden. Darüber hinaus muss der Abstand zwischen der jeweiligen Mitte zweier benachbarter Bahnen mindestens der 4-fachen Bahnbreite entsprechen. Taktleitungen sollten statt parallel eher senkrecht zu den Signalleitungen angeordnet werden und ordnungsgemäß terminiert werden, um Reflexionen zu minimieren. Zur Reduzierung der Kopplung müssen Single-Ended-Signale auf unterschiedlichen, senkrecht zueinander angeordneten Lagen platziert werden.

Zur Verbesserung der Signalintegrität müssen die Bahnen gerade und möglichst kurz sein. Werden gekrümmte Bahnen verwendet, sind 45°-Bogen zu nutzen und rechte Winkel zu vermeiden. Die Taktsignale müssen auf einer Lage platziert werden (liegt diese im Inneren, muss sie sich zwischen zwei Bezugsebenen befinden), welche zur Minimierung von Reflexionseffekten korrekt terminiert wurde und frei von Durchkontaktierungen ist, da diese zu Schwankungen bei Impedanz und Reflexionen führen können. Die Massefläche sollte ebenfalls so nah wie möglich an der Außenlage platziert werden, um das Rauschen zu reduzieren. Falls die Bahnen anstelle von Single-Ended-Signalen Differenzialpaar-Signale tragen, muss zwischen den Differenzialpaar-Bahnen derselbe Abstand eingehalten werden und die Bahnen müssen immer dieselbe Länge haben.

Zur Reduzierung des Ground Bounce existieren mehrere Techniken, darunter:

- Verwendung kurzer und breiter Bahnen zwischen Durchkontaktierungen und Kondensator-Pads;

- Möglichst kurze und breite Bahnen zwischen Stromanschluss und Power Supply-Ebene, um Impedanz und Spannungsabfall zu verringern;

- Jeden Anschluss bzw. jede Durchkontaktierung einzeln mit der Massefläche verbinden, um Reiheschaltungen zu vermeiden;

- Für jedes Paar aus VCC/GND-Signalen einen Entkopplungskondensator ergänzen und nahe an den zugehörigen Anschlüssen platzieren. Außerdem Kondensatoren mit niedrigem ESR und ESL wählen, um die Induktivität zu reduzieren.

- Universelle I/O-Signale dürfen niemals offen bleiben oder erdfrei sein, sondern müssen als mit Erde oder VCC verbundene Ausgangssignale konfiguriert werden.

und erhalten Sie innerhalb von 10 Minuten ein Angebot für Ihr PCBA-Projekt

Fazit

Zur Gewährleistung der Signalintegrität, einer hohen elektromagnetischen Kompatibilität und eines korrekten Wärmemanagements unter allen Betriebsbedingungen muss beim Design von Leiterplatten für Hochfrequenzsignale die korrekte Auswahl der Materialien und die Festlegung von Lagenaufbau, Leiterbahnen-Routing und Masse-, Power- und Signalebenen berücksichtigt werden.